# Supertex inc.

## 14W Off-line LED Driver, 120VAC, PFC, 14V, 1.0A Load

## **Specifications**

| Parameter                | Value                                                    |

|--------------------------|----------------------------------------------------------|

| AC line voltage          | 100 - 135VAC                                             |

| LED (string) voltage     | 0 - 14V                                                  |

| LED current              | 1.0A                                                     |

| Switching frequency      | 70 - 120kHz                                              |

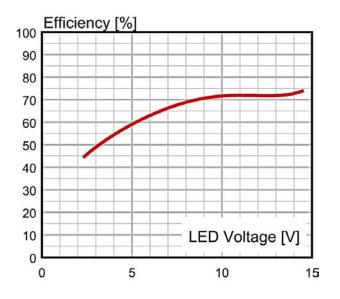

| Efficiency               | 74% (@ 14V)                                              |

| Open circuit protection  | Yes (output voltage 33V)                                 |

| Short circuit protection | Yes (output current 1.0A)                                |

| AC line undervoltage     | LED and AC line current fall off gradually below 100 VAC |

| Light dimmer compatible  | No                                                       |

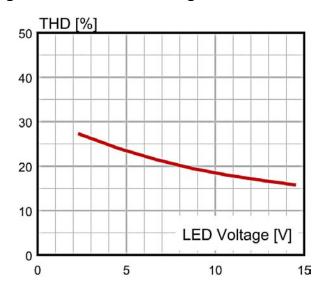

| THD                      | ~16% (LED voltage 14V)                                   |

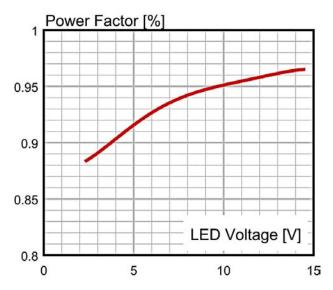

| Power factor             | >95% (LED voltage 14V)                                   |

## **General Description**

This Design Note describes the results of a 14W LED Driver Design. The design specifically forgoes the use of electrolytic capacitors, which form a point of weakness in high reliability and high ambient temperature applications.

The design drives one or more high brightness LEDs, in parallel or series combinations, at a current of 1.0A and up to a voltage of 14V. This same design can be operated at lower voltage/power levels as well, with slight loss of efficiency and THD.

The results, in particular the waveforms, documented in this note apply more broadly, i.e. at other output currents and voltage levels when appropriate adjustments are made to the size and value of certain components.

Efficiency can be increased by using components having less ohmic resistance, particularly L1 and M1, and by lowering the switching frequency.

The input line current features low harmonic distortion, satisfying the requirements of EN 61000-3-2 Class C (Lighting Equipment). Open circuit and in short circuit at the output can be sustained indefinitely. The AC line current is limited to an input voltage range from zero to 135VAC. Both the output current and line current drop gradually as AC line voltage falls below 100VAC.

Please refer to application note AN-H52 for a detailed description of and design guidance for the HV9931LED driver control IC.

## **Miscellaneous Notes**

### **EMI, Common Mode Filtering:**

The magnitude and frequency dependency of the common mode current on the line input depends heavily on physical layout and location of the LED driver circuit and the attached load. As such, the design may or may not require the addition of a common mode choke ahead of the bridge rectifier.

#### **Open Circuit Operation**

During open circuit operation the HV9931 is made to run at minimum duty cycle through the action of CS2 and ZOV. Some energy transfer, as small as it may be, still occurs, which causes the voltage on C1, and thereby the peak drain voltage on M1, to rise to a higher level. Circuit losses keep this raise in check. From experimental data: peak  $V_{C1}$  rises by about 35V from 120 to 155V, and maximum  $V_{DS}$  rises by 60V from 270 to 330V. If this rise is undesirable, a zener diode or a bleeder resistor can be placed across C1 to limit the voltage rise across C1 and M1, or more sophisticated circuitry can be added to further limit switching activity.

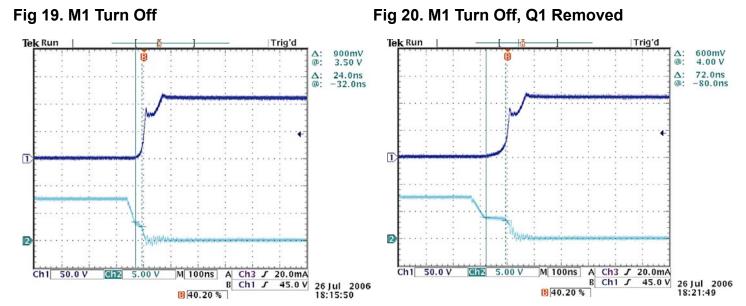

#### M1 Turn Off

An external pull down transistor was added to the gate drive circuit to speed up the turn off transition. Note that M1's drain current, which is more or less triangular in shape, is largest at turn off. Figures 19 and 20 illustrate the gain in turnoff speed that can be attained by this simple addition. Measurements showed an increase in efficiency by 0.5% from 73.2 to 73.7%, corresponding to a reduction in switching loss of 100mW. The small gain in efficiency may not warrant the addition of the pull down transistor, but may nevertheless be interesting when power levels are higher or a larger MOSFET having more gate and reverse transfer capacitance is in use.

#### V<sub>DD</sub> at Zero Crossing

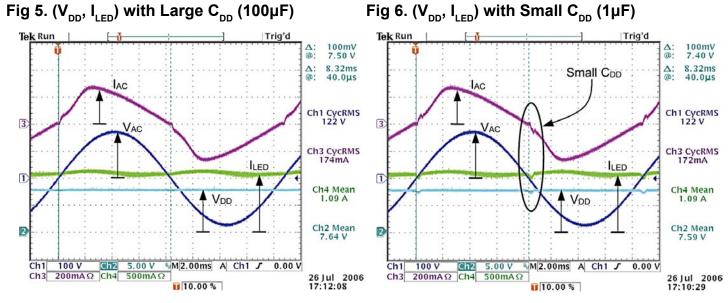

$V_{\rm DD}$  may drop out at the AC line zero crossings, and cause a short lived drop in LED current if the capacitor at the VDD pin is made small. If this effect is undesirable, then the  $C_{\rm DD}$  should be chosen sufficiently large. Figures 5 and 6 demonstrate this effect.

#### **CS1** Programming

Control of M1 should, under regular circumstances, be governed by the action of comparator CS2, which provides regulation of the LED current. CS1 should regulate only if limitation of input stage current is necessary, as during AC line undervoltage or during transient conditions. CS1 is to remain inactive by programming an envelope for the input stage current with an adequate margin, such that CS1 does not interfere with the regulation of the output current under normal circumstances. A simple DC threshold of adequate value will suffice.

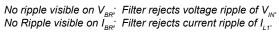

This design employs a somewhat more sophisticated envelope for the purpose of limiting the AC line current when undervoltage occurs. The threshold is a scaled version of the input voltage, thus reducing input current as input voltage reduces. By proper choice of values, CS1 will thus become active for input voltages lower than 100VAC, and take over regulation by limiting input stage current to an approximate sinusoidal waveform. For line voltages larger than 100V, this scaled threshold will become unnecessarily accommodative, and zener diode  $Z_{\text{REF1}}$  will limit its rise.

#### Diodes D1 and D2

D1 and D2 are part of the RT oscillator circuit which determines the switching frequency, or more precisely, the off-time  $(T_{OEE})$  of the switching period. The off time is determined by the oscillator discharge current which should appear when M1 is turned off, i.e. when the GATE pin is low. The main contribution to the discharge current is due to current in RT when the voltage at the GATE pin is low. Current originating at the RFF resistor is meant to modulate this discharge current in order to affect an increase or decrease of Tore. Note that RFF is driven by the ripple voltage across C1. As such, RFF carries an alternating current, which is present regardless of the timing needs of the RT pin. D1 and D2 resolve two issues depending on the polarity of the RFF current. When RFF sources current, it will overdrive the pin when GATE is high, which is undesirable. Diode D2 blocks this current, and the current will follow an the path through RT and the GATE pin. When RFF sinks current, diode D1 sources this current during the time that the RT discharge current should be zero (GATE pin high).

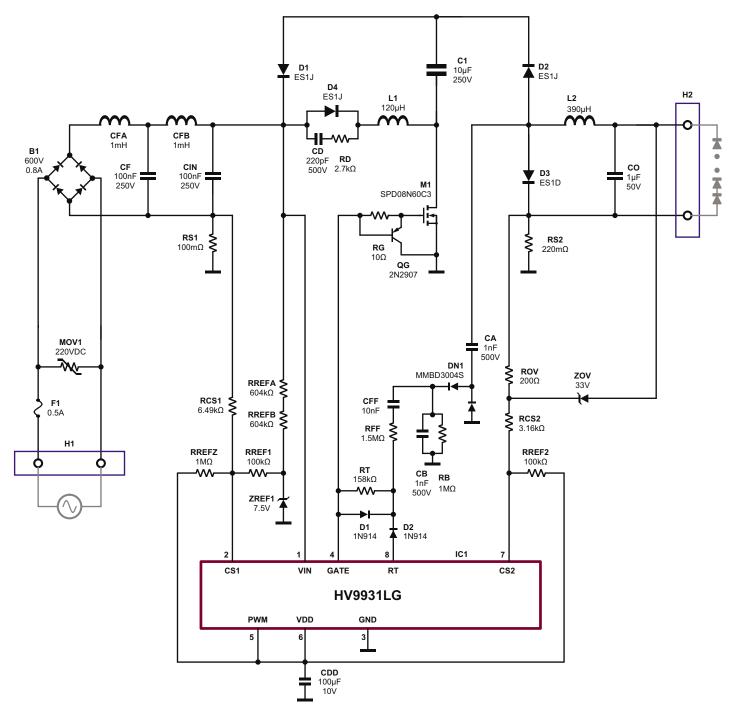

## **Schematic 1**

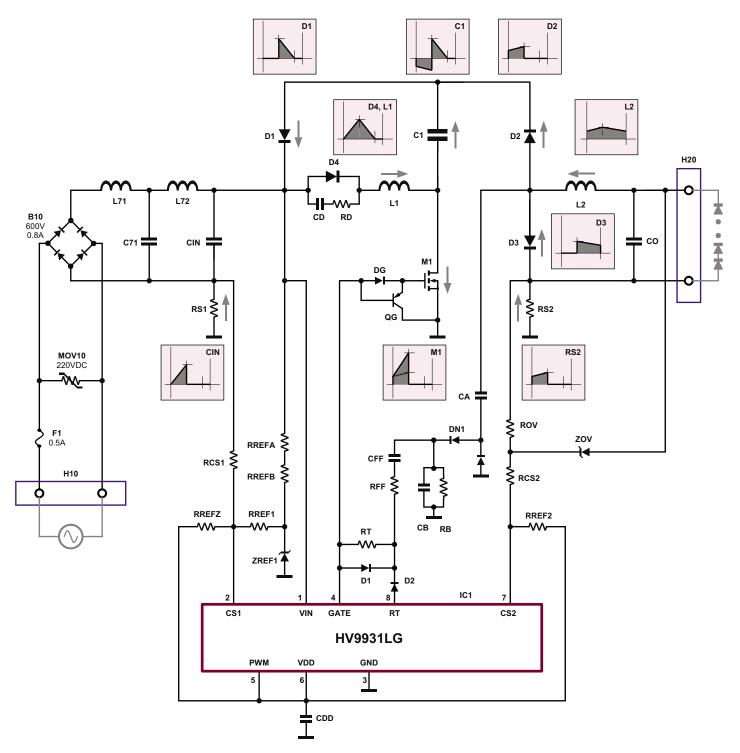

## Schematic 2

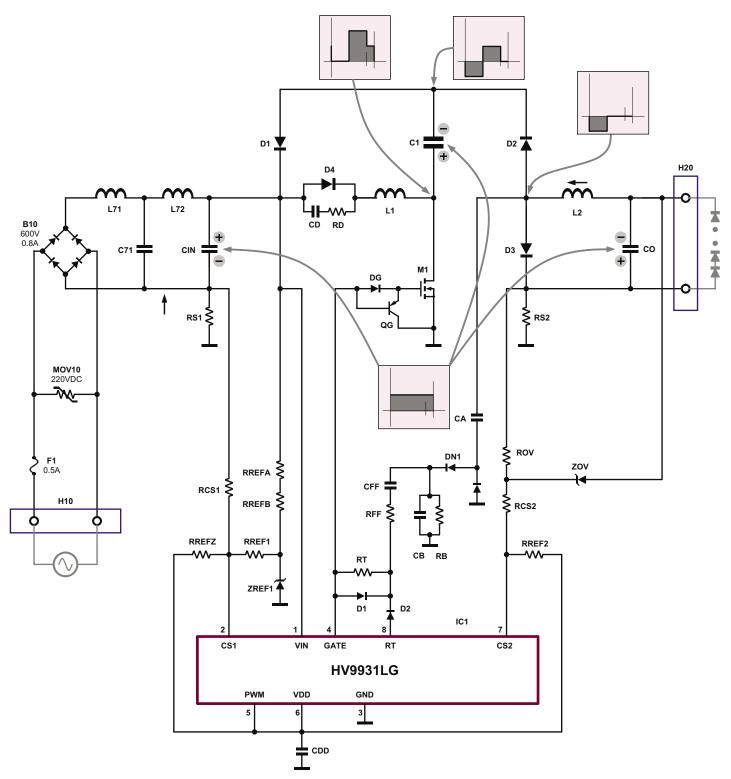

## Schematic 3

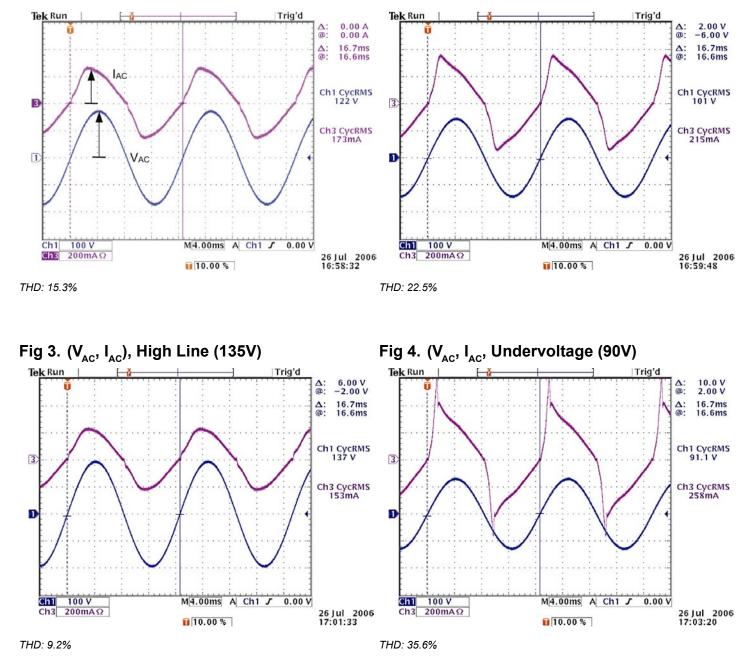

Fig 2. (V<sub>AC</sub>, I<sub>AC</sub>), Low Line (100V)

Much smaller  ${\rm C}_{\rm \tiny DD}$  is feasible, if slight loss of regulation at the zero crossings is acceptable.

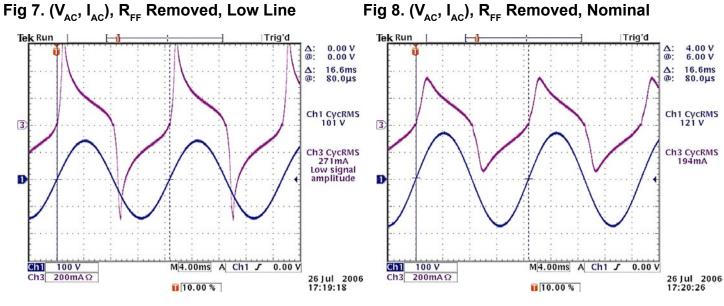

THD: Increases to 54.1% (from 22.5%)

THD: Increases to 31.5% (from 15.3%)

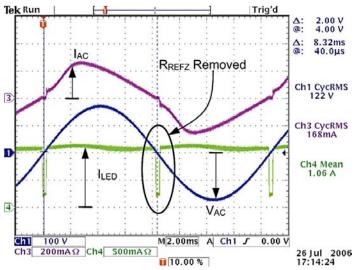

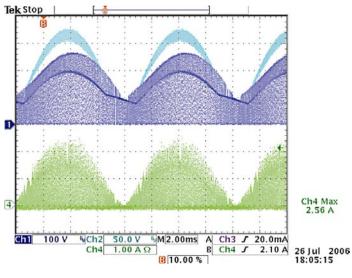

Fig 9.  $(I_{LED}, I_{AC}, V_{AC})$  when  $R_{REFZ}$  Removed

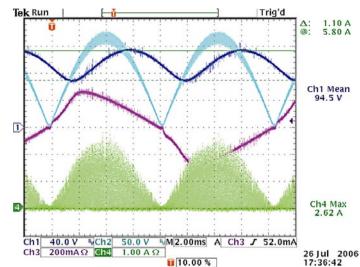

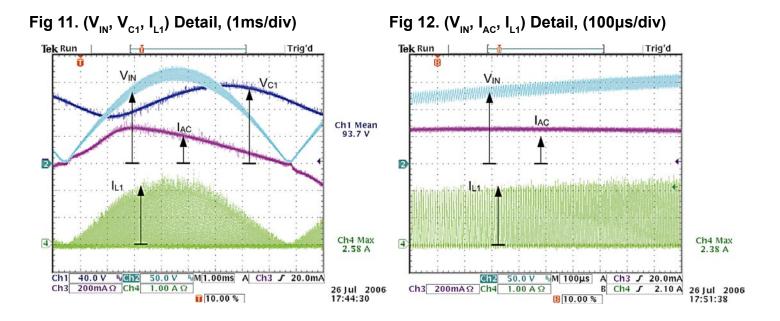

Fig 10. ( $V_{IN}$ ,  $V_{C1}$ ,  $I_{L1}$ ) Detail, (2ms/div)

$R_{\rm \tiny REF3}$  is needed to prevent loss of  $I_{\rm \tiny LED}$  regulation at the zero crossings, where CS1 not receive adequate bias from V  $_{\rm \tiny IN}$

Fig 13. ( $V_{IN}$ ,  $I_{AC}$ ,  $I_{L1}$ ) Detail, (10µs/div)

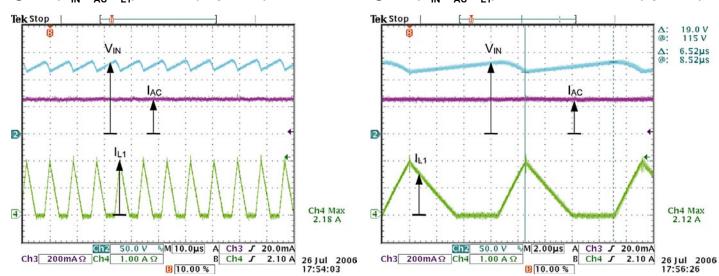

Fig 14. ( $V_{IN}$ ,  $I_{AC}$ ,  $I_{L1}$ ) Detail, Time Base (2µs/div)

Fig 15. M1 Drain Voltage, (2µs/div)

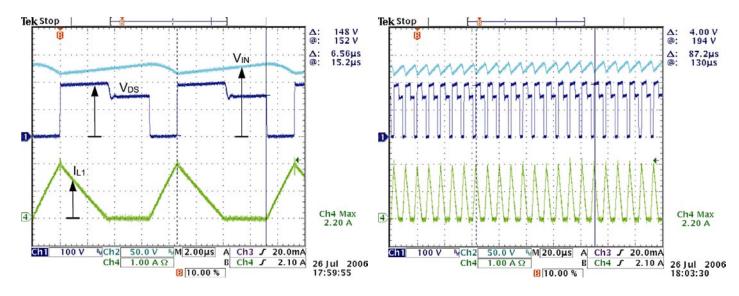

Fig 16. M1 Drain Voltage, (20µs/div)

### Fig 17. M1 Drain Voltage, (2ms/div)

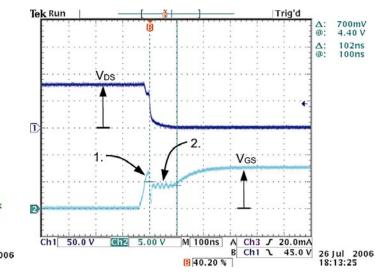

#### Fig 18. M1 Turn on

1.  $V_{GS}$  rises steadily; Diode D3 recovers. 2.  $V_{GS}$  plateaus; Miller effect due to falling  $V_{DS}$ .

V<sub>GS</sub> plateau about 25ns. Gate turn-off assisted by external PNP pull down transistor

Slower turn-off.  $V_{\rm gs}$  plateau about 70ns. Pull down transistor Q1 removed, and Zero $\Omega$  RG.

Limit never exceeds DC level,

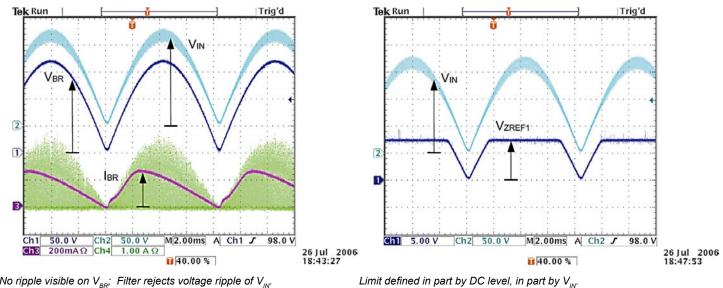

Fig 21. Input Filter Detail,  $(V_{IN}, V_{BR}, I_{BR})$

Fig 22. CS1 Programming Detail, V<sub>ZREF1</sub>

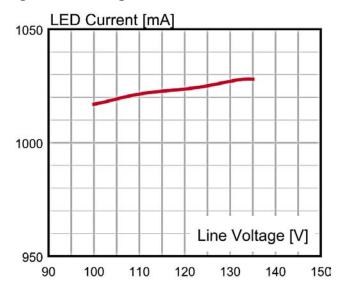

#### Fig 23. Line Regulation

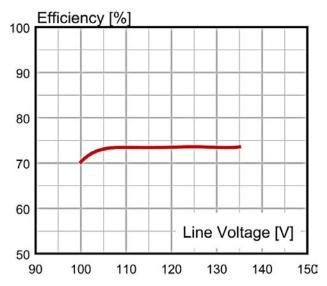

Fig 24. Efficiency vs Line Voltage

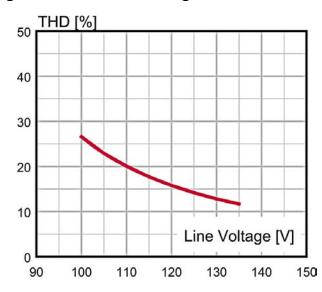

Fig 25. THD vs Line Voltage

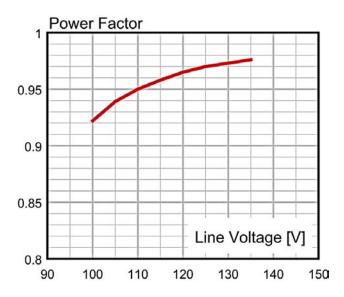

Fig 26. Power Factor vs Line Voltage

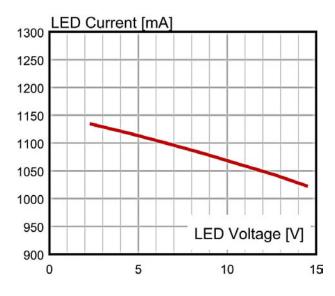

#### Fig 27. Load Regulation

#### Fig 28. Efficiency vs Load Voltage

Fig 29. THD vs Load Voltage

Fig 30. Power Factor vs Load Voltage

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the Supertex inc. website: http://www.supertex.com.

©2009 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.

1235 Bordeaux Drive, Sunnyvale, CA 94089 Tel: 408-222-8888 www.supertex.com