# Supertex inc.

# MD2130 Ultrasound Beamforming Transmitter Demoboard

#### Introduction

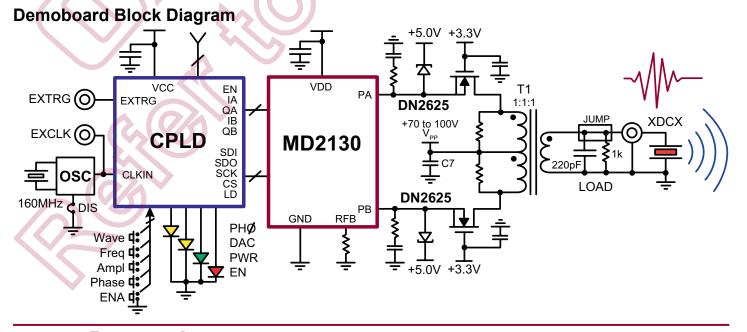

The MD2130 is a high-speed, arbitrary waveform, push-pull source-driver. It is designed for medical ultrasound imaging and HIFU beamforming applications. It also can be used in NDT, sonar and other ultrasound phase-array focusing beamforming applications.

The integrated circuit (IC) consists of the CMOS digital logic input circuits, an 8-bit current DAC for the waveform amplitude control, and four PWM current-sources. These current sources are constructed with the high-speed inphase and quadrature current-switch matrix and the built-in sine and cosine angle-to-vector look-up table. The angular resolution of the vector table is 7.5 degrees per step with a total range of 48 steps. There are four logic input signals to control the in-phase and quadrature PWM push-pull current-source's output timing frequency cycle in the burst and waveform envelope.

The MD2130's output stage is designed to drive two depletion mode high voltage DN2625 N-type MOSFETs as the source-drivers. The MOSFET drains are connected to a center-tap ultrasound frequency pulse transformer. The secondary winding of the transformer can connect to the ultrasound piezo or capacitive transducer via cable and with a good impendence match. The MD2130 has a high-speed serial data interface that quickly updates the data register's per-scan-line for changing the beamforming phase angles and apodization amplitudes.

#### **General Description**

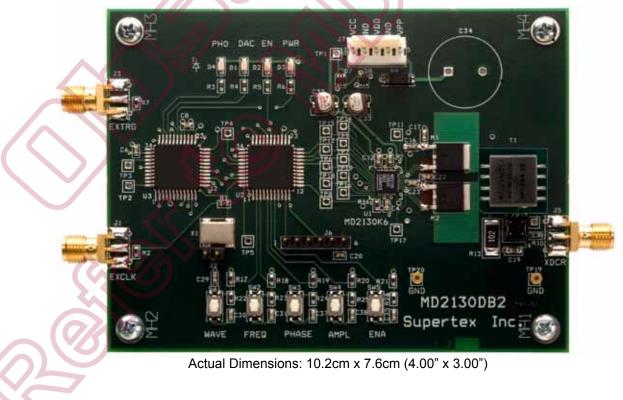

This demoboard datasheet describes how to use the MD2130DB2 to generate the ultrasound transmit beamforming waveform with the Gaussian profile, and the adjustable frequency, amplitude and phase angle. It also provides information about how to design a user application circuit and PCB using the MD2130 and DN2625 devices.

The MD2130DB2 circuit uses two depletion mode high voltage DN2625 MOSFETs in the push-pull mode to drive the center-tap wideband ultrasound output transformer. The MOSFETs are in a D-PAK surface mount package. The sources of the MOSFETs are directly driven by MD2130's two outputs, whose maximum peak sinking current is up to 3A. These current-source outputs are controlled by the MD1230's internal angular vector switch matrix and the in-phase and quadrature PWM input signals.

All the MD2130's logic control signals are generated by two small CPLD programmable logic circuits clocked by an on board 160MHz crystal oscillator. The CPLD circuits not only generate accurate timing for the high-speed PWM control waveforms, but also the serial data and clock to set and change the waveform amplitude DAC and phase angles data registers. The external clock input can be used if the on-board oscillator is disabled. The external trigger input can be used to synchronize the burst waveforms' launch timing. There are five push buttons for enabling and selecting the output waveform frequency, phase angle and amplitude.

Four color LEDs indicate the power, chip enable and waveform parameter selection states. The MD2130DB2 output waveform can be displayed by using an oscilloscope and the high impedance probe at the TP13 test point. It also can use an SMA to BNC 50 $\Omega$  coaxial cable connecting to oscilloscope directly, with an attenuation of 5:1 if R10 is 200 $\Omega$ . A cable can also be used to drive the user's transducer directly. Jumper J4 can be used to select whether or not to connect the on-board equivalent-load, which is formed by a 220pF capacitor in parallel with a 1k $\Omega$  resistor.

#### **Circuit Design & PCB Layout**

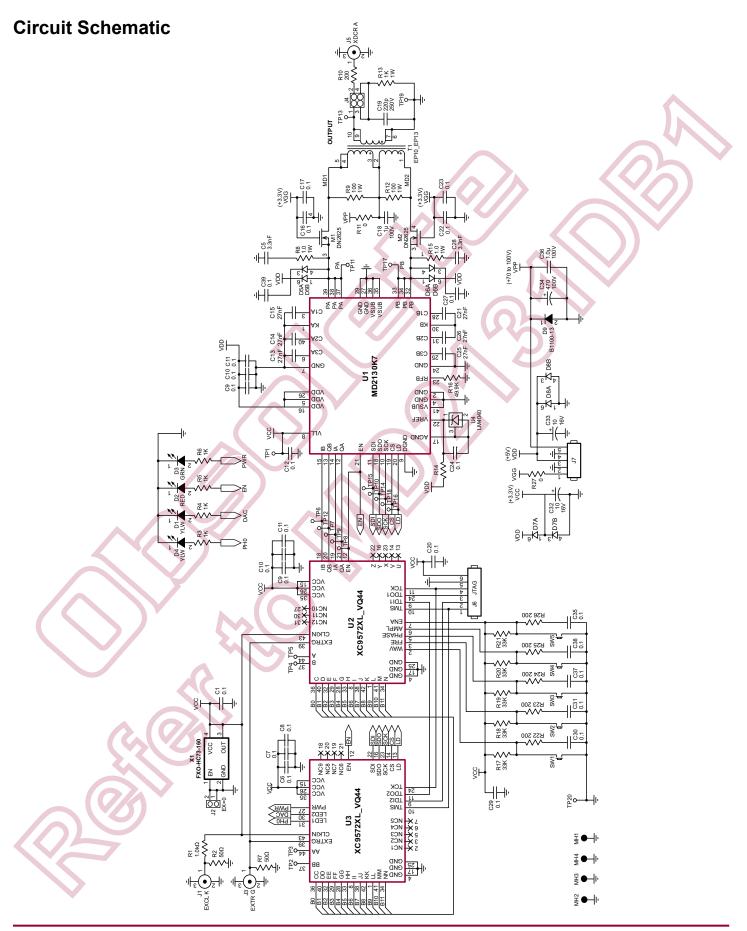

The thermal pad at the bottom of the MD2130 package must be connected to the V<sub>SUB</sub> pin on the PCB. The V<sub>SUB</sub> is connected to the IC's substrate. It is important to make sure that the V<sub>SUB</sub> is always at the highest potential of the IC circuit, in any condition, even during the power-up or down periods. That is why a proper supply voltage power-up sequence is needed to test the circuit. To prevent any supply voltage polarity reversing, the circuit also has the protection Schottky diodes D7, D8 and D9.

Due to the high current and high current slew rate nature of this common-gate, source-driven and push-pull circuit topology, the two cascading N-channel MOSFETs need to have very low lead inductance. The Supertex DN2625K7 is designed for this application and works seamlessly with the MD2130K7. In particular, a good PCB layout design needs to shorten the traces between the MD2130K7 output pins and the DN2625K7 source pins. It is also necessary to connect all three pairs of pins between them for the high current carrying capacity. Furthermore, because of the high di/dt in the output current of the MD2130, it is also necessary to have the Schottky diodes D5 and D6 from the driver output pins to the +5V power supply line as the clamping diodes. Note that the diodes must have enough speed and peak current capability. The RC snubber circuits of R8-C5 and R15-C28 at the output pins can dump the current pulse edge ringing effectively.

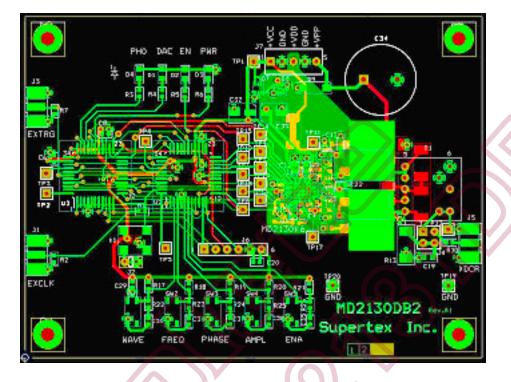

PCB designers need to pay attention to some of the connecting traces as high-voltage and high-speed traces. In particular, low capacitance to the ground plane and more trace spacing need to be applied in this situation.

High-speed PCB trace design practices that are compatible with about 100 to 200 MHz operating speed are used for the demoboard PCB layout. The internal circuitry of the MD2130 can operate at quite a high frequency, with the primary speed limitation being load capacitance. Because of this high speed and the high transient currents that result when driving even very small inductive loads, ringing and even oscillations are possible. The supply voltage bypass capacitors and the MOSFET gate de-coupling capacitors should be as close to the pins as possible. The capacitor's ground pin pads should have low inductance feed-through connections that are connected directly to a solid ground plane. The V<sub>DD</sub> and V<sub>PP</sub> supplies can draw fast transient currents of up to 3.5A, so they should be provided with a low-impedance bypass capacitor at the chip's pins. A ceramic capacitor of 0.1 to 1.0µF may be used. Minimize the trace length to the ground plane, and insert a ferrite bead in the power supply lead to the capacitor to prevent resonance in the power supply lines. For applications that are sensitive to jitter and noise and using multiple MD2130 ICs, insert another ferrite bead between V<sub>pp</sub> and decouple each chip supply separately. Pay particular attention to minimizing trace lengths and using sufficient trace width to reduce inductance not only on the supply pins but also on the CA/B KA/B compensation pins. Very closely placed surface mount components are highly recommended. Be aware of the parasitic coupling from the high voltage outputs to the input signal terminals of MD2130. This feedback may cause oscillations or spurious waveform shapes on the edges of signal transitions. Since the input operates with signals down to 1.8V, even small coupling voltages may cause problems. Use of a solid ground plane and good power and signal layout practices will prevent this problem. Also ensure that the circulating ground return current from a capacitive load cannot react with common inductance to create noise voltages in the input logic circuitry.

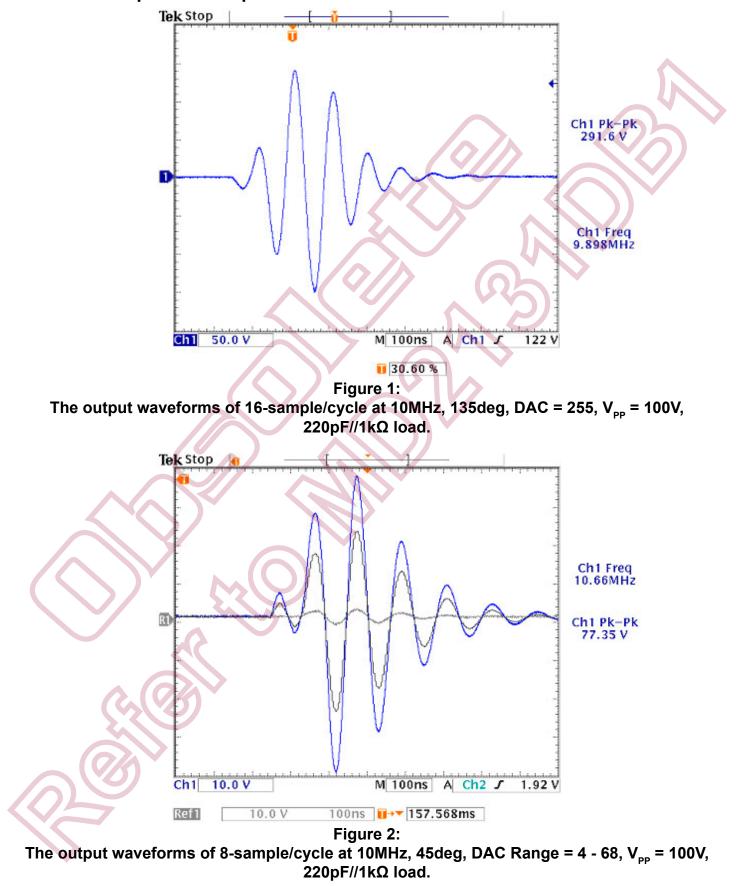

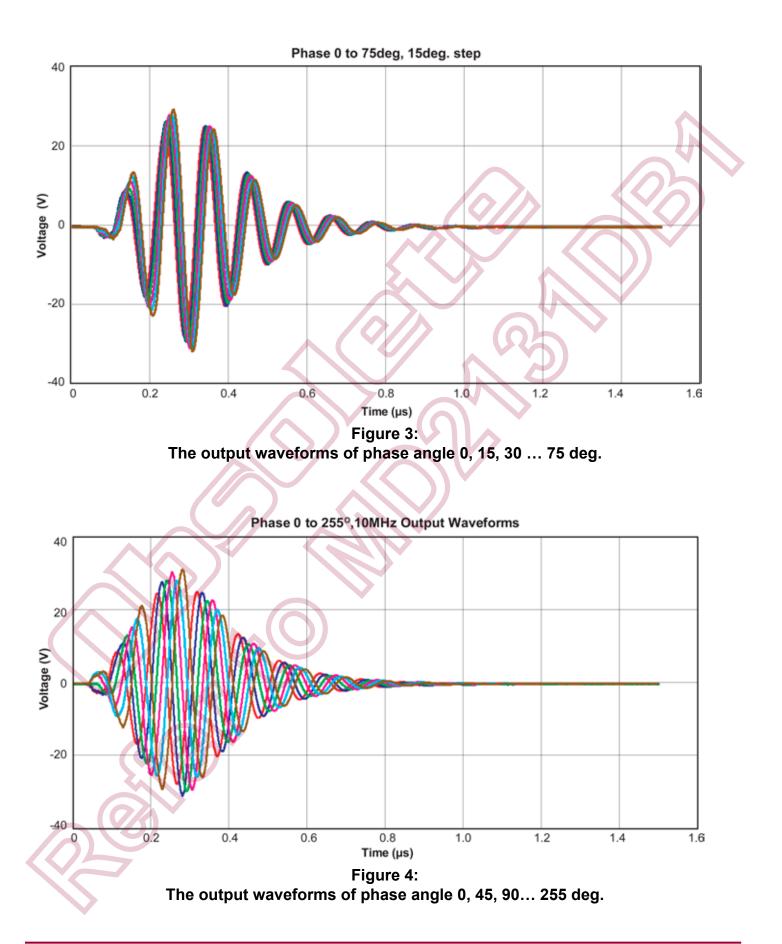

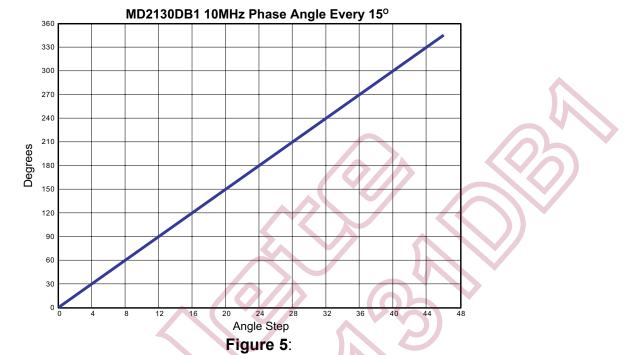

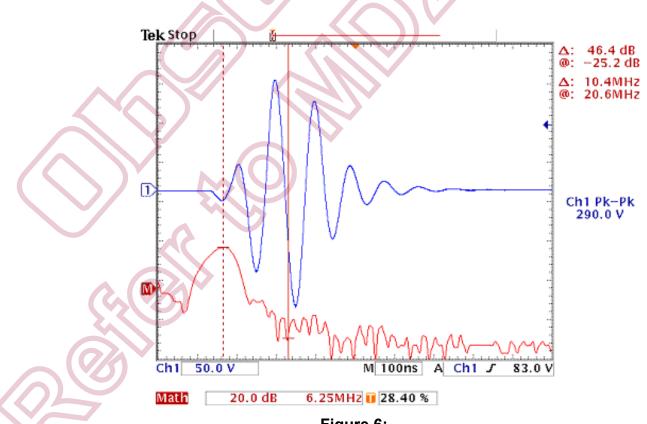

This MD2130DB2 beamforming demoboard should be powered up with multiple DC power supplies with current limiting functions. The power supply voltages and current limits used in the testing are listed on page 7. There are examples of the MD2130DB2 demoboard input and output waveform and measurements shown in Figures 1 to 7.

#### **Output Transformer Design**

There is a center tap wideband ultrasound transformer needed for the push pull output circuit. The transformer serves at least three functions: the balanced differential to singleend RF output transformer; the isolation barrier to the ultrasound probe; and the impedance matching or low-pass network combined with the cable and transducer element. The MD2130 PWM clock may operate at a 40MHz to 160MHz frequency range, however the wideband transformer only needs to work in the frequency band of the ultrasound being transmitted. Beside the bandwidth consideration, the transformer also needs enough peak-current capacity and RF power coupling efficiency to make sure the ferrite magnetic core will not be saturated, have little leakage inductance and a small size.

Supertex inc. • 1235 Bordeaux Drive, Sunnyvale, CA 94089 • Tel: 408-222-8888 • www.supertex.com

#### **PCB** Layout

MD2130DB2

#### MD2130DB2 Input and Output Waveforms

The phase angle measurements of 10MHz, 15 deg/step from 24 traces of 10,000 data points FFT. The maximum MD2130 phase angular resolution is 7.5deg.

Figure 6: The 10MHz 16 sample/cycle output waveform and FFT (Math) results at 10MHz and harmonics,  $220pF//1k\Omega$  load.

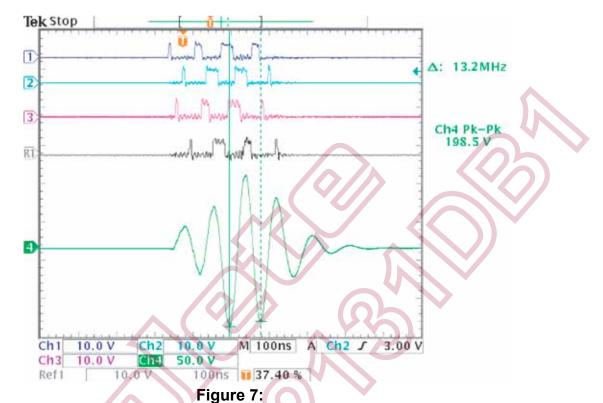

Input IA, IB, QA, QB and load waveform of RF 13.3 MHz, 12-sample/cycle, 160MHz PWM.

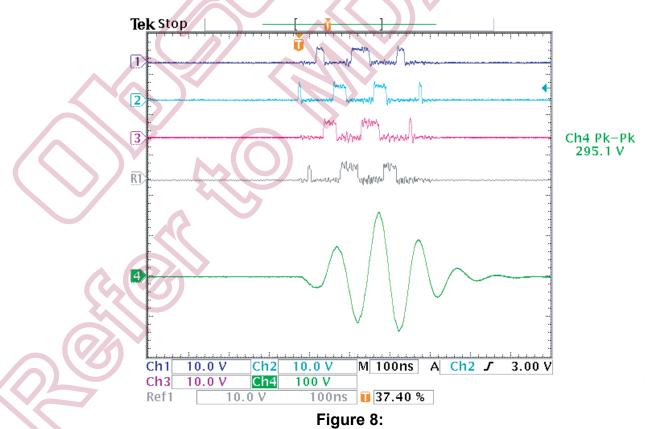

Input IA, IB, QA, QB and load waveform of RF 10MHz, 16-sample/cycle, 160MHz PWM.

Figure 9:

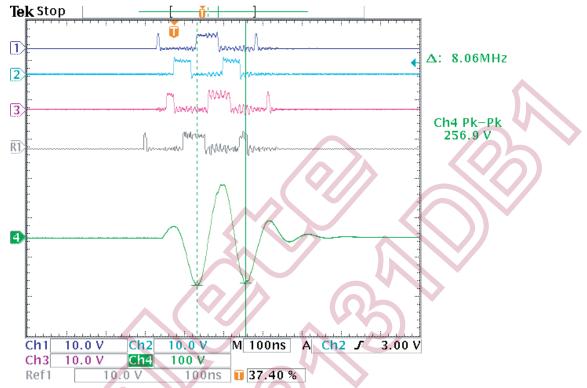

Input IA, IB, QA, QB and load waveform of RF 8.0MHz, 20-sample/cycle, 160MHz PWM..

### **Output Waveform Frequency Selection Table**

| Output    | Samples / Cycle of Ultrasound Output Waveform |         |        | Note:                       |  |

|-----------|-----------------------------------------------|---------|--------|-----------------------------|--|

| Frequency | 12 s/c                                        | 16 s/c  | 20 s/c | NOLE:                       |  |

| Frequency | 13.3MHz                                       | 10.0MHz | 8.0MHz | f <sub>CLKIN</sub> = 160MHz |  |

### **Output Waveform Phase Angle Selection Table**

|                          | Note |     |       |     |                              |

|--------------------------|------|-----|-------|-----|------------------------------|

| 0                        | 1    | 24  | 47    | 48  | Note                         |

| 0<br>(power-on, LED1 on) | 7.5  | 180 | 352.5 | 360 | Output<br>Phase Angle Degree |

### **Output Waveform Amplitude Selection Table**

| Amplitude Steps (AMPL Button) |    |                               |     |     | Note               |  |

|-------------------------------|----|-------------------------------|-----|-----|--------------------|--|

| 0                             | 1  | 8                             | 15  | 16  | Note               |  |

| 0                             | 16 | 128<br>(power-on,<br>LED2 on) | 240 | 255 | DAC Register Value |  |

# **Board Connector and Test Pin Description**

| CPLD               | Signal Name   | Description                                              |  |

|--------------------|---------------|----------------------------------------------------------|--|

| Pin #              |               |                                                          |  |

| U2,3-15,26,35      | VLL           | Logic Power Supply +3.3V                                 |  |

| U2,3-4,17,25       | GND           | Logic Power Ground 0V                                    |  |

| U2-2               | WAV           | Run or stop demo waveform phase                          |  |

| U2-3               | FRE           | Selecting frequency: 8,10 and 13.3MHz                    |  |

| U2-5               | PHASE         | Single step phase change, Angle stepping:0, 7.5, 15360   |  |

| U2-6               | AMPL          | Single step amplitude change, DAC stepping: 15, 31255    |  |

| U2-7               | ENA           | Control MD2130 EN pin                                    |  |

| U2-18              | IA            | Output signal to MD2130 IA                               |  |

| U2-19              | IB            | Output signal to MD2130 IB                               |  |

| U2-20              | QA            | Output signal to MD2130 QA                               |  |

| U2-21              | QB            | Output signal to MD2130 QB                               |  |

| U3-31              | LED1          | Output signal Yellow, PH0 LED is on when Phase = 0       |  |

| U3-30              | LED2          | Output signal Yellow, DAC LED is on when DAC = 127       |  |

| U3-27              | PWR           | Output signal LED Green, indicates +3.3V power supply on |  |

| U2,3-10            | TMS           | Test Mode Select of JTAG                                 |  |

| U2,3-9             | TDI           | Test Data In of JTAG, two CPLD in daisy chain            |  |

| U2,3-24            | TDO           | Test Data Out of JTAG, two CPLD in daisy chain           |  |

| U2,3-11            | тск           | Test Clock of JTAG                                       |  |

| U2,3-43            | CLK           | CPLD clock input                                         |  |

| U2,3-39            | EXTRG         | External trigger signal input to control waveform timing |  |

| U2,3-12            | EN            | Output signal LED Red, indicates MD2130 is enabled       |  |

| U3-22              | SDI           | Output signal to MD2130 SDI                              |  |

| U3-16              | SDO           | Input signal from MD2130 SDO                             |  |

| U3-23              | SCK           | Output signal to MD2130 SCK                              |  |

| U3-14              | CS            | Output signal to MD2130 CS                               |  |

| U3-13              | LD            | Output signal to MD2130 LD                               |  |

| All remaining pins | <u>n. (7)</u> | NC or Reserved                                           |  |

# **CPLD Programming Connector**

| JTAG Pin # | Signal Name     | Description                                       |   |

|------------|-----------------|---------------------------------------------------|---|

| J6-1       | TMS             | Test mode select of CPLD                          |   |

| J6-2       | TDI             | Test data In of CPLD                              |   |

| J6-3       | TDO             | Test data out of CPLD                             |   |

| J6-4       | ТСК             | Test clock of CPLD                                |   |

| J6-5       | GND             | Logic power supply ground 0V for programming only | 5 |

| J6-6       | V <sub>cc</sub> | Logic power supply +3.3V for programming only     |   |

# **Test Signal Connector**

| SMA &<br>Jumper | Signal Name | Description                                                                                       |

|-----------------|-------------|---------------------------------------------------------------------------------------------------|

| J1              | EXCLK       | External clock input when on-board oscillator is disabled, or output the clock when it is enabled |

| J2              | OSC_EN      | Jumper for on-board oscillator, short = disable, open = enabled                                   |

| J3              | EXTRG       | External trigger signal input, 0V to 3.3V Square Wave, 10KHz to 40KHz only                        |

| J4              | Load JP     | Jumper for on-board RC load to MD2130DB2 high voltage output and XDCR connector                   |

| J5              | XDCR        | MD2130DB2 waveform output, for SMA-cable to oscilloscope, high voltage!<br>0 to +/-350Vp-p max    |

# Power Supply Connector

| Power<br>Supply Pin # | Signal Name     | Description                                                          |

|-----------------------|-----------------|----------------------------------------------------------------------|

| J7-1                  | V <sub>cc</sub> | +3.3V, CPLD control logic supply voltage with current limit to 250mA |

| J7-2                  | GND             | Ground reference, 0V                                                 |

| J7-3                  | V <sub>DD</sub> | +5V MD2130 positive supply voltages with current limit to 50mA       |

| J7-4                  | GND             | Ground reference, 0V                                                 |

| J7-5                  | V <sub>PP</sub> | +70 to100V, the high voltage supply with current limit to 30mA       |

# **Voltage Supply Power-Up Sequence**

| Step       | Signal Name        | Description                                                          |  |

|------------|--------------------|----------------------------------------------------------------------|--|

| 1          | V <sub>DD</sub>    | +5.0, MD2130 positive supply voltages                                |  |

| 2          | V <sub>cc</sub>    | +3.3V, MOSFET gate biasing and CPLD control logic supply voltage     |  |

| 3          | V <sub>PP</sub>    | +70V to 100V, the high voltage supply                                |  |

| 4          | EN<br>Logic Active | nable logic control, active-high signal to MD2130                    |  |

| Power-Down |                    |                                                                      |  |

| 1          | EN<br>Logic Active | Disable logic control, active-high signal to MD2130                  |  |

| 2          | V <sub>PP</sub>    | +70V to 100V, the high voltage supply, off                           |  |

| 3          | V <sub>DD</sub>    | +5V, MD2130 positive supply voltages with all input signals LOW, off |  |

| 4          | V <sub>cc</sub>    | +3.3, CPLD control logic supply voltage with EN=0, off               |  |

#### MD2130DB2 Bill of Materials

| Reference  | Description                                                           | Manufacturer     | Manufacturer's<br>Part Number |

|------------|-----------------------------------------------------------------------|------------------|-------------------------------|

| C1-12      | CAP .1µF 25V CERAMIC X7R 0603                                         | NA               | Any                           |

| C13,14,15  | CAP .027µF 50V CERAMIC X7R 0603                                       | ECJ-1VB1H273K    | Panasonic                     |

| C18, C36   | CAP CER 1µF 100V X7R 20% 1210                                         | C3225X7R2A105M   | TDK                           |

| C19        | CAP CERAMIC 220PF 200V NP0 0805                                       | ECJ-2YC2D221J    | Panasonic                     |

| C32, C33   | CAP 10µF 16V ELECT WT SMD                                             | UWT1C100MCL1GB   | Nichicon                      |

| C5, C28    | CAP CER 3300PF 10% 100V X7R 0603                                      | 06031C332KAT2A   | AVX                           |

| C34        | CAP 470µF 100V ELECT VR RADIAL                                        | UVR2A471MHD      | Nichicon                      |

| D1-4       | LED RED, GREEN, YELLOW DIFF 0805 SMD                                  | NA               | Any                           |

| D9         | DIODE SCHOTTKY 100V 1A SMA                                            | B1100-13         | Diodes Inc                    |

| D5-8       | DIODE SCHOTTKY DUAL 30V SOT-363                                       | BAT54DW-7        | Diodes Inc                    |

| M1, M2     | DEPLETION 250V 3.0A N-MOSFET IN D-PAK                                 | DN2625K4         | Supertex Inc                  |

| R1-4       | RES 1/16W 1% 0603 SMD                                                 | NA               | Any                           |

| R8,9,12,15 | RES 1W 1% 2512 SMD                                                    | NA               | Any                           |

| T1         | L <sub>w</sub> = 22µH, 1:1:1 WIDEBAND ULTRASOUND<br>PULSE TRANSFORMER | 750340727        | Würth Electronics             |

| U1         | IC ULTRASOUND BEAMFORMING SOURCE<br>DRIVER 5X5MM QFN-40               | MD2130K7         | Supertex Inc.                 |

| U2, U3     | IC CPLD 72 MCELL C-TEMP 44-VQFP                                       | XC9572XL-5VQ44C  | Xilinx                        |

| U4         | IC PREC MICROPWR REF SOT-23                                           | LM4040DEM3-2.5   | National                      |

| X1         | OSC CLOCK 160.000 MHZ 3.3V SMD                                        | JITO-2-DC3AE-160 | FOX Electronics               |

| <b>Supertex inc.</b> does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| an adequate "product liability indemnification insurance agreement." <b>Supertex inc.</b> does not assume responsibility for use of devices described, and limits its liability |

| to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and                  |

| specifications are subject to change without notice. For the latest product specifications refer to the <b>Supertex inc.</b> (website: http://www.supertex.com)                 |

©2011 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.