# **High Voltage Dual EL Lamp Driver**

#### **Features**

- ▶ Independent input control for lamp selection

- Split supply capability

- Patented output timing

- One miniature inductor to power both lamps

- Low shutdown current

- ▶ Wide input voltage range 2.0 to 5.8V

- Output voltage regulation

- ► No SCR output

- Available in small packages (10-Lead DFN and MSOP)

#### **Applications**

- Mobile cellular phones, dual display

- Keypad and LCD backlighting

- Portable instrumentation

- Dual segment lamps

- ► Hand held wireless communication devices

#### **General Description**

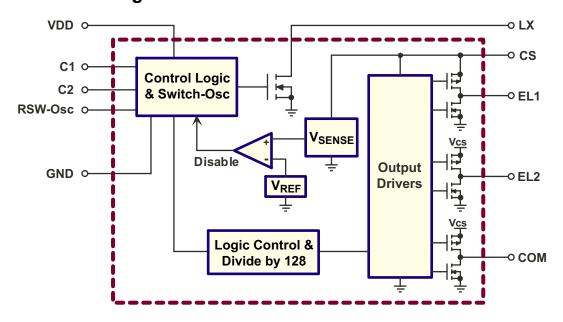

The Supertex HV841 is a high voltage driver designed for driving two EL lamps with a combined area of 3.5 square inches. The input supply voltage range is from 2.0V to 5.8V. The device is designed to reduce the amount of audible noise emitted by the lamp. This device uses a single inductor and minimum number of passive components to drive two EL lamps. The nominal regulated output voltage of ±100V is applied to the EL lamps. The chip can be enabled/ disabled by connecting C1 and C2 (pins 1 and 4) to VEN/ Ground.

The HV841 has an internal oscillator, a switching MOSFET, and two high voltage EL lamp drivers. An external resistor connected between the RSW-Osc and the voltage supply pin VDD sets the frequency for the switching MOSFET. The EL lamp driver frequency is set by dividing the MOSFET switching frequency by 128. An external inductor is connected between the LX and the VDD pins. Depending on the EL lamp size, a 1.0 to 10.0nF, 200V capacitor is connected between CS and Ground. The two EL lamps are connected between EL1 to COM and EL2 to COM.

The switching MOSFET charges the external inductor and discharges it into the capacitor at CS. The voltage at CS increases. Once the voltage at CS reaches a nominal value of 100V, the switching MOSFET is turned off to conserve power. The outputs EL1 to COM and EL2 to COM are configured as H bridges and switch in opposite states to achieve 200V across the EL lamp.

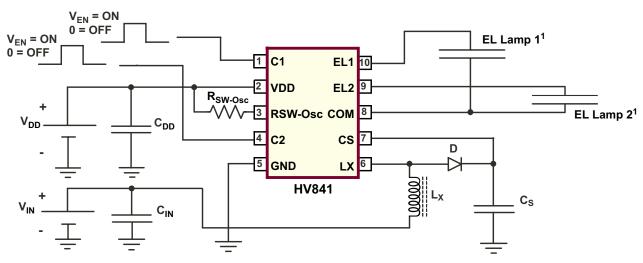

## **Typical Application Circuit**

1 The bigger sized lamp should be tied to EL1 and the smaller sized lamp to EL2 terminals (pins 10 and 9 respectively)

### **Ordering Information**

|        | Package Options                                                        |                                                                         |  |  |  |  |  |  |  |

|--------|------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Device | 10-Lead DFN<br>3.00x3.00mm body<br>1.00mm height (max)<br>0.50mm pitch | 10-Lead MSOP<br>3.00x3.00mm body<br>1.10mm height (max)<br>0.50mm pitch |  |  |  |  |  |  |  |

| HV841  | HV841K6-G                                                              | HV841MG-G                                                               |  |  |  |  |  |  |  |

<sup>-</sup>G indicates package is RoHS compliant ('Green')

## **Absolute Maximum Ratings**

| Parameter                           | Value          |

|-------------------------------------|----------------|

| Supply voltage, V <sub>DD</sub>     | -0.5 to +7.5V  |

| Supply voltage, V <sub>CS</sub>     | -0.5 to +120V  |

| Operating ambient temperature range | -40°C to +85°C |

| Storage temperature range           | -65° to +150°C |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground, GND

#### **Thermal Resistance**

| Package       | $oldsymbol{	heta_{ja}}$ |

|---------------|-------------------------|

| 10-Lead DFN*  | 60°C/W                  |

| 10-Lead MSOP* | 400°C/W                 |

<sup>\*</sup> Mounted on FR4 board, 25mm x 25mm x 1.57mm

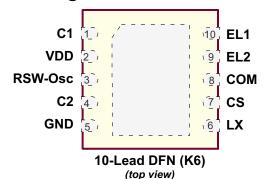

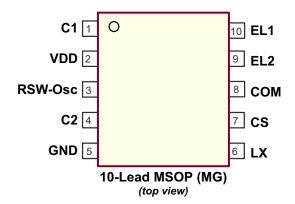

### **Pin Configurations**

(Pads are on the bottom of the package.)

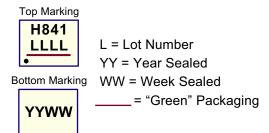

#### **Product Marking**

Y = Last Digit of Year Sealed W = Code for Week Sealed L = Lot Number

\_\_ = "Green" Packaging

10-Lead DFN (K6)

10-Lead MSOP (MG)

#### **Recommended Operating Conditions**

| Sym             | Parameter             | Min | Тур | Max | Units | Conditions |

|-----------------|-----------------------|-----|-----|-----|-------|------------|

| V <sub>DD</sub> | Supply voltage        | 2.0 | -   | 5.8 | V     |            |

| T <sub>A</sub>  | Operating temperature | -40 | -   | 85  | °C    |            |

#### **Electrical Characteristics**

**DC Characteristics** (Over operating conditions unless otherwise specified,  $T_A$ = 25°C)

| Sym                 | Parameter                                                         | Min  | Тур  | Max             | Units | Conditions                                 |

|---------------------|-------------------------------------------------------------------|------|------|-----------------|-------|--------------------------------------------|

| R <sub>DS(ON)</sub> | On-resistance of switching transistor                             | -    | -    | 6.0             | Ω     | I = 100mA                                  |

| V <sub>DD</sub>     | Input voltage range                                               | 2.0  | -    | 5.8             | V     |                                            |

| V <sub>cs</sub>     | Output regulation voltage                                         | 90   | 100  | 110             | V     | V <sub>DD</sub> = 2.0V to 5.8V             |

| V <sub>DIFF</sub>   | Differential output peak to peak voltage (EL1 to COM, EL2 to COM) | 180  | 200  | 220             | V     | V <sub>DD</sub> = 2.0V to 5.8V             |

|                     | Quiescent VDD cumply current                                      | -    | -    | 150             | nA    | $C_1 = C_2 = 0 \text{ to } 0.1V$           |

| DDQ                 | Quiescent VDD supply current                                      | -    | -    | 500             | nA    | $C_1 = C_2 = 0.1 \text{ to } 0.3 \text{V}$ |

| I <sub>DD</sub>     | Input current into the VDD pin                                    | -    |      | 190             | μΑ    | V <sub>DD</sub> = 2.0V to 5.8V             |

| f <sub>EL</sub>     | V <sub>DIFF</sub> output drive frequency                          | 215  | 244  | 273             | Hz    | V <sub>IN</sub> = 3.0V. See Figure 1.      |

| f <sub>sw</sub>     | Switching transistor frequency                                    | 27.5 | 31.2 | 34.9            | kHz   | V <sub>IN</sub> = 3.0V. See Figure 1.      |

| D                   | Switching transistor duty cycle                                   | 85   | -    | 89              | %     |                                            |

| I <sub>IL</sub>     | Input logic low current going into the control pin                | -    | -    | -0.6            | μА    | V <sub>DD</sub> = 2.0V to 5.8V             |

| I <sub>IH</sub>     | Input logic low current going into the control pin                | -    | -    | 0.6             | μΑ    | V <sub>DD</sub> = 2.0V to 5.8V             |

| V <sub>EN-L</sub>   | Logic input low voltage                                           | 0    | -    | 0.3             | V     |                                            |

| V <sub>EN-H</sub>   | Logic input high voltage                                          | 1.5  | -    | V <sub>DD</sub> | V     |                                            |

### **Function Table**

| C <sub>1</sub> | C <sub>2</sub> | EL,  | $EL_2$ | СОМ  | IC  |

|----------------|----------------|------|--------|------|-----|

| 0              | 0              | Hi Z | Hi Z   | Hi Z | OFF |

| 0              | 1              | Hi Z | ON     | ON   | ON  |

| 1              | 0              | ON   | Hi Z   | ON   | ON  |

| 1              | 1              | ON   | ON     | ON   | ON  |

### **Functional Block Diagram**

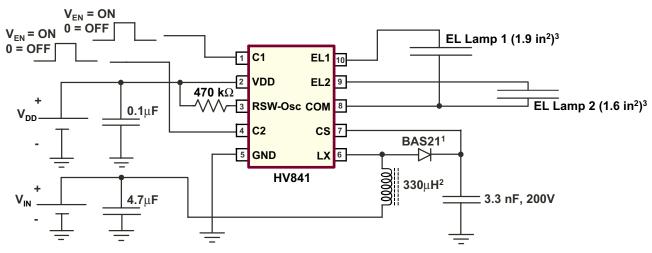

### **Figure 1: Test Circuit**

- 1 or any (equivalent or better) > 120V, fast recovery diode

- 2 Murata LQH4CN331K04

- 3 The bigger sized lamp should be tied to EL1 and the smaller sized lamp to EL2 terminals (pins 10 and 9 respectively)

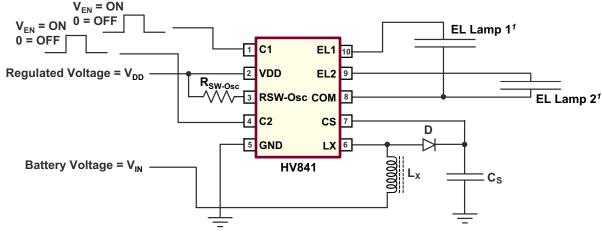

#### **Split Supply Configuration**

The HV841 can be used in applications operating from a battery where a regulated voltage is available. This is shown in Figure 2. The regulated voltage can be used to drive the internal logic of HV841. The amount of current used to drive

the internal logic is less than 190µA. Therefore, the regulated voltage could easily provide the current without being loaded down.

Figure 2: Split Supply Configuration

1. The bigger sized lamp should be tied to EL1 and the smaller sized lamp to EL2 terminals (pins 10 and 9 respectively)

#### **Audible Noise Reduction**

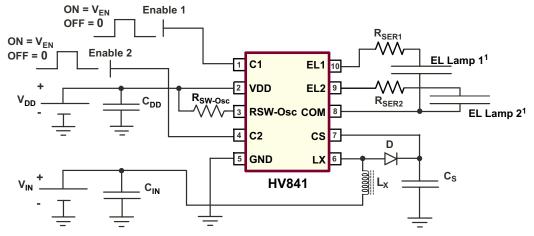

This section describes a method (patented) developed at Supertex to reduce the audible noise emitted by the EL lamps used in application sensitive to audible noise. The waveform takes the shape of approximately 2RC time constants for rising and 2RC time constants for falling, where C is the capacitance of the EL lamp, and R is the external resistor,  $R_{\mbox{\tiny SEP}}$  connected in series with the EL lamp.

Figure 3 shows a general circuit schematic that uses the series resistors,  $R_{\rm SER1}$  and  $R_{\rm SER2}$ , for each of the EL lamps.  $R_{\rm SER1}$  and  $R_{\rm SER2}$  are connected in series with the EL lamp. The audible noise can be set a desirable level by selecting the resistances for  $R_{\rm SER1}$  and  $R_{\rm SER2}$ . It is important to note that addition of these external resistors will reduce the voltage across the EL lamp, and hence the brightness of the EL lamp.

Figure 3: Typical Application Circuit For Audible Noise Reduction

The bigger sized lamp should be tied to EL1 and the smaller sized lamp to EL2 terminals (pins 10 and 9 respectively)

# **Pin Configuration and Description**

| Pin# | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | C1      | Enable input signal for EL lamp 1. Logic high will turn ON the EL lamp 1 and logic low will turn it OFF. Refer to the Function Table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2    | VDD     | Input supply voltage pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3    | RSW-Osc | External resistor connection to set both the switching MOSFET frequency and EL Lamp frequency. The external resistor should be connected between this pin and the VDD pin. The EL lamp frequency is switching frequency divided by 128. The switching frequency increases as the value of $R_{\text{SW-Osc}}$ decreases. A 470k $\Omega$ resistor will provide a switching frequency of 31.2 kHz, and an EL lamp frequency of 244 Hz. To change the frequency to $f_{\text{SW}}$ , the value of the resistor $R_{\text{SW-Osc}}$ can be determined as $R_{\text{SW-Osc}}$ = (470k x 31.2k) / $f_{\text{SW}}$ .                                                                                                                                    |

| 4    | C2      | Enable input signal for EL lamp 2. Logic high will turn ON the EL lamp 2 and logic low will turn it OFF. Refer to the Function Table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5    | GND     | IC Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6    | LX      | External inductor connection to boost the low input voltage using inductive flyback. Connect an inductor between VIN and this pin. Also connect a high voltage fast recovery diode between this pin and the CS pin. The anode of the diode needs to be connected to the LX pin and the cathode to the CS pin. In general, small valued inductors, which can handle more current, are more suitable for driving large sized lamps. As the inductor value decreases, the switching frequency should be increased to avoid saturation. When the switching MOSFET is turned ON, the inductor is being charged. When the MOSFET is turned OFF, the energy stored in the inductor is transferred to the high voltage capacitor connected at the CS pin. |

| 7    | CS      | Connect a 200V capacitor between this pin and GND. This capacitor stores the energy transferred from the inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8    | COM     | Common connection for both EL lamps. Connect one end of both the lamps to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9    | EL2     | EL lamp 2 connection. For optimum performance, the smaller of the two lamps should be connected to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10   | EL1     | EL lamp 1 connection. For optimum performance, the larger of the two lamps should be connected to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

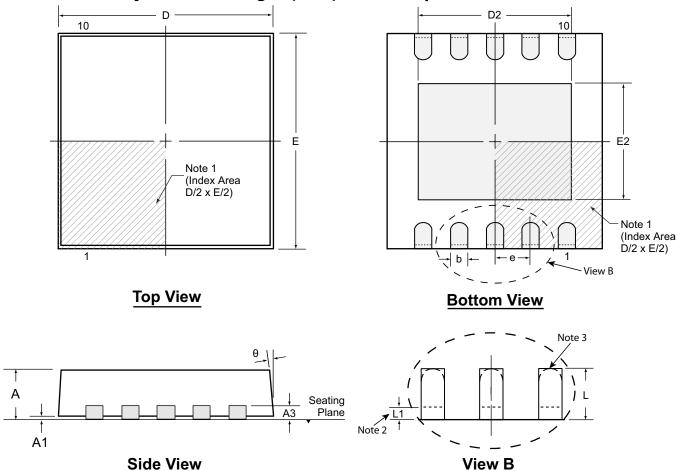

# 10-Lead DFN Package Outline (K6)

## 3.00x3.00mm body, 1.00mm height (max), 0.50mm pitch

#### Notes:

- 1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Depending on the method of manufacturing, a maximum of 0.15mm pullback (L1) may be present.

- 3. The inner tip of the lead may be either rounded or square.

| Symb           | ol  | Α    | A1   | А3          | b    | D     | D2   | E     | E2   | е           | L    | L1    | θ          |

|----------------|-----|------|------|-------------|------|-------|------|-------|------|-------------|------|-------|------------|

| <b>.</b> .     | MIN | 0.80 | 0.00 |             | 0.18 | 2.85* | 2.20 | 2.85* | 1.40 | 0.50        | 0.30 | 0.00* | <b>0</b> º |

| Dimension (mm) | NOM | 0.90 | 0.02 | 0.20<br>REF | 0.25 | 3.00  | -    | 3.00  | -    | 0.50<br>BSC | 0.40 | -     | -          |

| (mm)           | MAX | 1.00 | 0.05 | 11          | 0.30 | 3.15* | 2.70 | 3.15* | 1.75 | 1 1000      | 0.50 | 0.15  | 14°        |

JEDEC Registration MO-229, Variation VEED-5, Issue C, Aug. 2003.

\* This dimension is not specified in the original JEDEC drawing. The value listed is for reference only.

Drawings not to scale.

Supertex Doc. #: DSPD-10DFNK63X3P050, Version A101008.

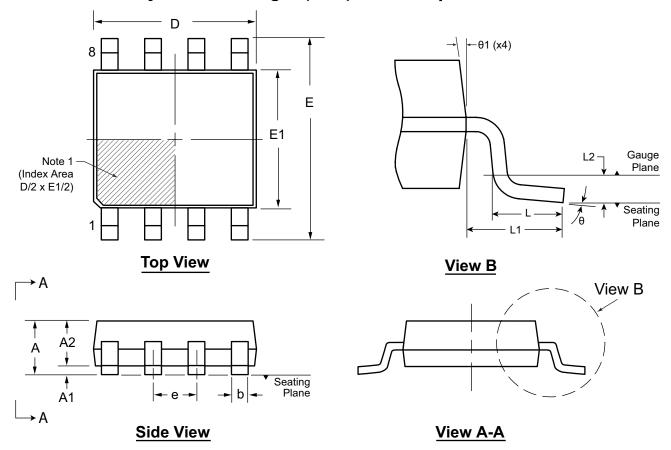

# 8-Lead MSOP Package Outline (MG)

# 3.00x3.00mm body, 1.10mm height (max), 0.65mm pitch

#### Note:

1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo          | ol  | Α     | <b>A</b> 1 | A2   | b    | D     | E     | E1    | е           | L    | L1          | L2          | θ          | θ1  |

|----------------|-----|-------|------------|------|------|-------|-------|-------|-------------|------|-------------|-------------|------------|-----|

|                | MIN | 0.75* | 0.00       | 0.75 | 0.22 | 2.80* | 4.65* | 2.80* |             | 0.40 |             |             | <b>0</b> º | 5°  |

| Dimension (mm) | NOM | -     | -          | 0.85 | -    | 3.00  | 4.90  | 3.00  | 0.65<br>BSC | 0.60 | 0.95<br>REF | 0.25<br>BSC | -          | -   |

| (111111)       | MAX | 1.10  | 0.15       | 0.95 | 0.38 | 3.20* | 5.15* | 3.20* |             | 0.80 |             |             | <b>8</b> º | 15° |

JEDEC Registration MO-187, Variation AA, Issue E, Dec. 2004.

Drawings are not to scale.

Supertex Doc. #: DSPD-8MSOPMG, Version G101008.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the Supertex inc. website: http://www.supertex.com.

©2008 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.

www.supertex.com

<sup>\*</sup> This dimension is not specified in the original JEDEC drawing. The value listed is for reference only.